Saagar Jha

(replying to Saagar Jha)

Saagar Jha

(replying to Saagar Jha)

Saagar Jha

(replying to Saagar Jha)

Saagar Jha

(replying to Saagar Jha)

Saagar Jha

(replying to Saagar Jha)

Saagar Jha

(replying to Saagar Jha)

Saagar Jha

(replying to Saagar Jha)

Saagar Jha

(replying to Saagar Jha)

Saagar Jha

(replying to Saagar Jha)

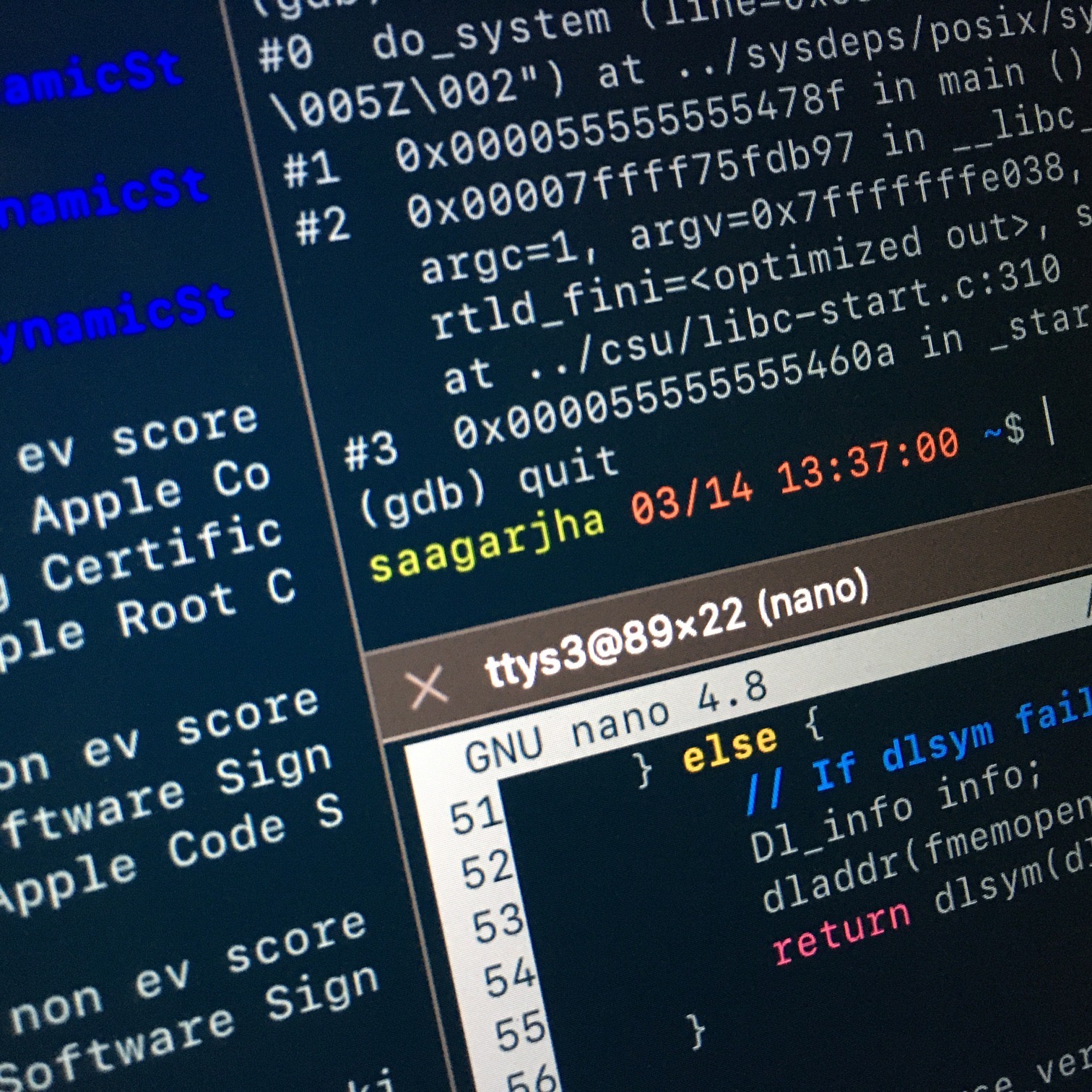

@dougall @marcan Anyways it’s probably needless to say that nobody really has answers here or bothers to do anything beyond the basics so it’s broken in all the debuggers that I know of. For example I found this when double checking something just now: https://discourse.llvm.org/t/aarch64-watchpoints-reported-address-outside-watched-range-adopting-mask-style-watchpoints/67660